# <u>A Mathematical</u> <u>Description of</u> <u>MOSFET Behavior</u>

Q: We've learned an awful lot about enhancement MOSFETs, but we still have yet to established a mathematical relationships between i<sub>D</sub>, v<sub>GS</sub>, or v<sub>DS</sub>. How can we determine the correct numeric values for MOSFET voltages and currents?

A: A mathematical description of enhancement MOSFET behavior is relatively straightforward! We actually need to concern ourselves with just **3 equations**.

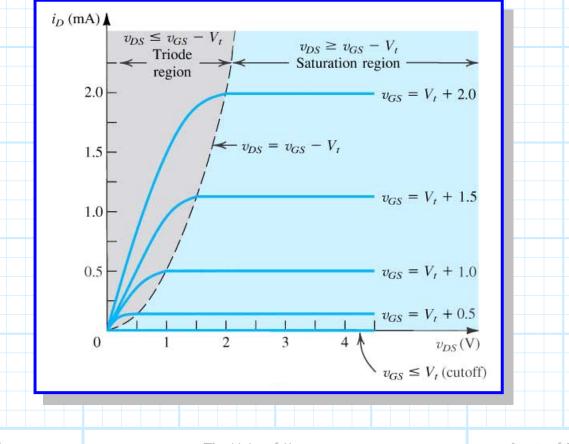

Specifically, we express the drain current  $i_D$  in terms of  $v_{GS}$  and  $v_{DS}$  for each of the **three MOSFET modes** (i.e., Cutoff, Triode, Saturation).

Additionally, we need to mathematically define the **boundaries** between each of these three modes!

But first, we need to examine some fundamental **physical parameters** that describe a MOSFET device. These parameters include:

$$k' \doteq$$

Process Transconductance Parameter  $\left\lceil A/V^2 \right\rceil$

$$\frac{N}{L}$$

= Channel Aspect Ratio

The Process Transconductance Parameter k' is a constant that depends on the process technology used to fabricate an integrated circuit. Therefore, all the transistors on a given substrate will typically have the **same value** of this parameter.

**The Channel Aspect Ratio** W/L is simply the ratio of channel width W to channel length L. This is the MOSFET device parameter that can be **altered** and **modified** by the circuit designer to satisfy the requirements of the given circuit or transistor.

We can likewise combine these parameter to form a **single** MOSFET device parameter *K* :

$$\boldsymbol{K} = \frac{1}{2} \boldsymbol{k}' \left( \frac{\boldsymbol{W}}{\boldsymbol{L}} \right) \qquad \qquad \left[ \boldsymbol{A}_{\boldsymbol{V}^2} \right]$$

Now we can mathematically describe the behavior of an enhancement MOSFET! Well do this **one mode at a time**.

This relationship is very simple—if the MOSFET is in **cutoff**, the drain current is simply **zero**!

$$i_D = 0$$

(CUTOFF mode)

## TRIODE

When in **triode** mode, the drain current is dependent on **both**  $v_{GS}$  and  $v_{DS}$ :

$$i_{D} = k' \left( \frac{W}{L} \right) \left[ \left( v_{GS} - V_{t} \right) v_{DS} - \frac{1}{2} v_{DS}^{2} \right]$$

(TRIODE mode)

$$= k \left[ 2 \left( v_{GS} - V_{t} \right) v_{DS} - v_{DS}^{2} \right]$$

This equation is valid for **both** NMOS and PMOS transistors (**if** in TRIODE mode). Recall that for **PMOS** devices, the values of  $v_{GS}$  and  $v_{DS}$  are **negative**, but note that this will result (correctly so) in a **positive** value of  $i_D$ .

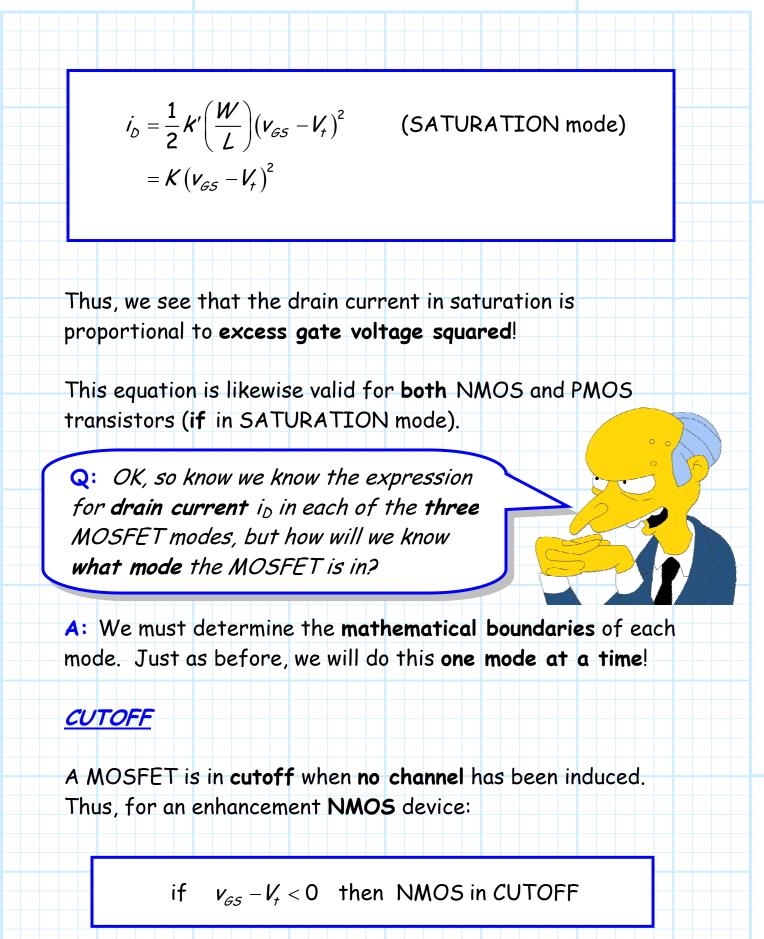

#### SATURATION

When in **saturation** mode, the drain current is (approximately) dependent on  $v_{GS}$  only:

Like wise, for an enhancement **PMOS** device:

if  $v_{GS} - V_{t} > 0$  then PMOS in CUTOFF

### TRIODE

For triode mode, we know that a channel **is** induced (i.e., an inversion layer is present).

Additionally, we know that when in triode mode, the voltage  $v_{DS}$  is not sufficiently large for NMOS, or sufficiently small (i.e., sufficiently negative) for PMOS, to pinch off this induced channel.

Q: But how large does v<sub>DS</sub> need to be to pinch off an NMOS channel? How can we determine **if** pinch off has occurred?

A: The answer to that question is surprisingly simple. The induced channel of an NMOS device is pinched off if the voltage  $v_{DS}$  is greater than the excess gate voltage! I.E.:

if  $v_{DS} > v_{GS} - V_t$  then NMOS channel is "pinched off"

if  $v_{DS} < v_{GS} - V_t$  then PMOS channel is "pinched off"

These statements of course mean that an NMOS channel is not pinched off if  $v_{DS} < v_{GS} - V_t$ , and a PMOS channel is not pinched off if  $v_{DS} > v_{GS} - V_t$ . Thus, we can say that an NMOS device is in the TRIODE mode:

if

$$v_{GS} - V_t > 0$$

and  $v_{DS} < v_{GS} - V_t$  then NMOS in TRIODE

Similarly, for PMOS:

if  $v_{GS} - V_t < 0$  and  $v_{DS} > v_{GS} - V_t$  then PMOS in TRIODE

#### SATURATION

Recall for SATURATION mode that a channel **is** induced, and that channel **is** pinched off.

if

$$v_{GS} - V_t > 0$$

and  $v_{DS} > v_{GS} - V_t$  then NMOS in SAT.

And for **PMOS**:

if  $v_{GS} - V_t < 0$  and  $v_{DS} < v_{GS} - V_t$  then PMOS in SAT.

We now can construct a **complete** (continuous) expression relating drain current  $i_D$  to voltages  $v_{DS}$  and  $v_{GS}$ . For an **NMOS** device, this expression is:

$$i_{D} = \begin{cases} 0 & \text{if } v_{GS} - V_{t} < 0 \\ \mathcal{K} \left[ 2 \left( v_{GS} - V_{t} \right) v_{DS} - v_{DS}^{2} \right] & \text{if } v_{GS} - V_{t} > 0 \text{ and } v_{DS} < v_{GS} - V_{t} \\ \mathcal{K} \left( v_{GS} - V_{t} \right)^{2} & \text{if } v_{GS} - V_{t} > 0 \text{ and } v_{DS} > v_{GS} - V_{t} \end{cases}$$

Likewise, for a **PMOS** device we find:

$$i_{D} = \begin{cases} 0 & \text{if } v_{GS} - V_{t} > 0 \\ \mathcal{K} \left[ 2 \left( v_{GS} - V_{t} \right) v_{DS} - v_{DS}^{2} \right] & \text{if } v_{GS} - V_{t} < 0 \text{ and } v_{DS} > v_{GS} - V_{t} \\ \mathcal{K} \left( v_{GS} - V_{t} \right)^{2} & \text{if } v_{GS} - V_{t} < 0 \text{ and } v_{DS} < v_{GS} - V_{t} \end{cases}$$

Let's take a look at what these expressions look like when we **plot** them. Specifically, for an NMOS device let's plot  $i_D$  versus  $v_{DS}$  for different values of  $v_{GS}$ :